NMOS의 제작과정

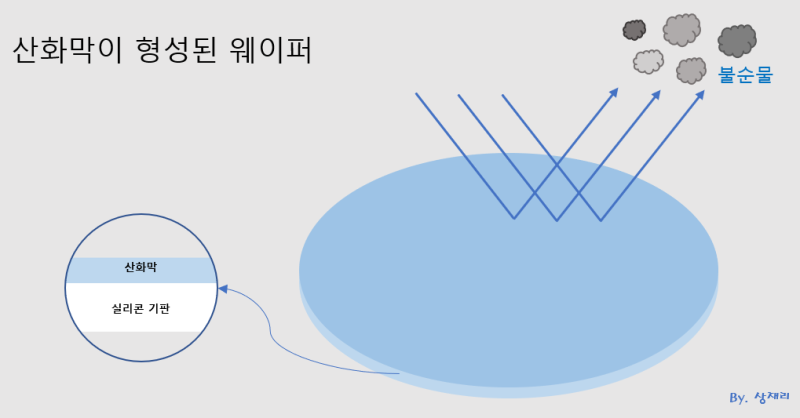

1. p-si에 oxidation을 통한 SiO2 (GI) 형성

2. poly-si 증착 (deposition)

3. etch

4. implantation (S,D 형성)

gate insulator와 substrate의 접합 (Si와 SiO2 접합)이 가장 중요하다.

oxidation furnace내에 O2나 H2O를 주입해서 oxidation을 발생시킨다.

1. Si+O2 + 고온(1000도) → SiO2 방식을 dry oxidation이라고 하며 더 얇게 만들 수 있다.

2. Si + 2H2O → SiO2 + 2H2 방식을 wet oxidation이라고 하며 수증기를 넣음으로써 더 빠르고 두껍게 만들 수 있다.

oxidation 공정을 진행하지 않을 때에는oxidation furnace 내에 질소를 계속 넣어서 내부에서 반응하지 못하도록 막고 있다.

SiO2는 결합각, 구조로 인해 amorphous 구조를 갖는다.

single구조의 Si 위에 비정질 구조의 SiO2를 길러내는 메커니즘을 갖기 때문에 실리콘을 소비하면서 점점 SiO2가 성장하게 되며 중간의 경계면을 기준으로 위쪽은 SiO2가 성장되고, 아래쪽은 Si를 소비하는 층이 만들어진다.

산화막 두께의 불균일성으로 인해 위쪽이 0.54tox, 아래쪽이 0.46tox을 갖는 것이 일반적이다. 이는 Si와 SiO2의 volume density 차이로 인해 발생한다.

SiO2의 장점

SiO2는 9.1eV의 에너지밴드갭을 갖고 1700도의 녹는점을 갖는다.

- resistivity > 10^17 : 전류를 매우 잘 막아준다.

- energy band gap >9 eV

- 10MV/cm : high breakdown E-field

- 경계면이 안정하다. (GI와 sub 사이)

- 재현성이 높다. (반복공정 시 항상 동일한 SiO2가 형성된다.)

- oxide 성장이 모든 방향으로 conformal 하게 성장한다. (일정하게 성장하며 방향성이 없다.)

- mask의 역할을 할 수 있다. 이는 원소들의 확산을 막아준다.

- etching selectivity (선택비 : 깎아내려는 물질과 아닌 물질의 비율)가 좋다. 불산 용액에 넣으면 SiO2만을 잘 제거할 수 있다.

forming gas annealing process

oxidation 공정 이후에 forming 공정을 진행하며 수소를 주입하여 dangling bond를 제거하는 역할을 한다.

forming gas: 5% H2 in N2 gas

이러한 공정에 있어서 dangling bond의 수를 줄이는 것이 중요하다.

dangling bond의 수 : 10^10 for <100> surface

dangling bond의 수 : 5*10^10 for <111> surface

따라서 반도체 산업에서는 dangling bond의 수가 더 적기 때문에 <100> wafer만을 이용한다.

Si와 SiO2의 경계면이 안정하기 때문에 최소한의 trap 수 (10^10 for <100> surface)를 갖는다. 만약 다른 물질(insulator)과 Si의 접합이 이루어지면 10배 이상의 dangling bond를 생성해 낼 것이다.

Deal-Grove model

Deal-Grove model을 통해 oxidation이 시간에 따라 어떻게 진행되는지 예측할 수 있다.

oxidant : 실리콘과 반응하는 oxide (산화제)

oxidation 초기구간 : tox 얇아서 금방 Si에 도달한다. interface의 반응에 의해 speed가 결정되며 t(두께)에 비례하여 성장한다.

시간이 많이 흐르면 diffusion으로 인해 t^1/2에 비례하여 oxide가 성장한다.

(온도를 증가시키면 log scale로 증가하며 exponential 하게 비례한다.)

Oxiation 공정의 문제점

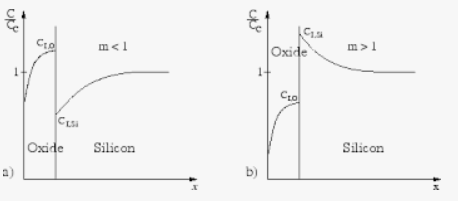

SiO2층을 GI로 사용하게 될 경우 도펀트들이 oxidation에 침투하는 현상이 발생한다.

이때 interface 근처에서 boron이 SiO2층으로 건너가며 Si 측 Boron이 줄어들게 된다. 이러한 현상은 원하는 Vt를 얻을 수 없게 한다.

따라서 oxidation을 할 때 도펀트가 재분배되는 상황도 고려하여 도핑해야 한다.

Ga 같은 도펀트는 oxidation 공정이 불가능하다. Ga이 oxide로 너무 빨리 빠져나가버리기 때문이다.

따라서 기판에 도핑을 할 때 도핑원소와 SiO2와의 반응성도 중요하다.

Oxidation 공정은 최신공정에서 쓰이지 않는다.

MOSFET이 scaling 됨이 따라 oxidation공정이 사용되지 않는다.

Gate와 Drain, Gate와 Source, 인접한 MOSFET과의 Cap 성분 등, 기생 Cap 성분이 많이 존재한다. 이것은 RC delay를 발생시킨다.

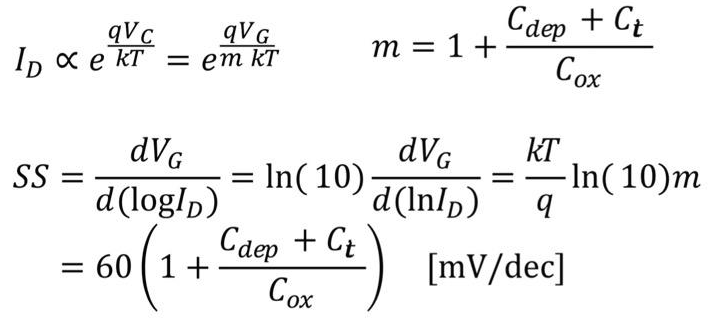

따라서 SS를 감소시켜 빠른 동작모드의 전환이 이루어지게 만드는 것이 중요하다. SS를 감소시키는 방법으로는 Cox를 증가시키는 방법이 있다.

하지만 현재 GI의 두께를 줄여서 SS를 낮추는 방식은 한계가 있다.

SiO2는 1.2nm두께가 한계이다. 더 얇아질 경우 전자가 tunneling 하는 현상이 발생하기 때문이다. 이는 누설전류로 이어진다.

따라서 SiO2의 층을 줄여서 Cox를 키우는 방법이 불가능하다.

그래서 생각해 낸 방법이 high K 물질을 사용하여 C를 증가시키는 것이다. 유전상수와 에너지 밴드갭은 반비례하는 경향이 있으며, 이로 인해 두께는 더 두꺼워지지만 더 높은 Cox를 얻을 수 있다.

만약 밴드갭이 너무 낮은 물질을 사용할 경우, 낮은 밴드갭을 뛰어넘어서 전자가 침투할 수 있다.

따라서 적절한 High-K 물질을 gate insulator로 선택하는 것이 중요하다.

'공정법' 카테고리의 다른 글

| Etching (0) | 2023.10.23 |

|---|---|

| Photolithography (1) | 2023.10.23 |

| Metallization _ Damascene Process (1) | 2023.10.23 |

| Sputter (1) | 2023.10.20 |