1T DRAM 이라고 부르기도 한다.

process와 memory차이의 performance 차이가 점점 심해지고 있고 memory 성능의 증가 폭이 크지않다.

process에서 빨리 처리하여도 memory에서 처리하는데 한계가 있다.

SRAM ← DRAM보다 10배이상 빠름 → DRAM으로 data를 옮김

SRAM은 chip의 면적은 많이차지한다.

전체적인 system의 speed를 높이긴 위해선 DRAM와 processer 사이의 물리적 거리를 최대한 줄이는 것이 solution이다.

같은 chip 내에서 만들면 DRAM과 CPU가 통합 → 더 빠른 연산속도를 얻을 수 있을 것이다. → Embedded DRAM 이라고 부른다. → 하지만 Cap 때문에 거의 불가능하다.

Cap에 전하가 있고 없고를 기준으로 data를 저장하기 때문에 cap의 scaling이 매우 어렵다.

어느정도 이상의 전하가 저장되어야 하기 때문이다. 따라서 최소한의 C 값을 만들어줘야 한다.

C= 앱실론*면적/거리 ← 면적이 어느정도 이상 항상 확보해야한다.

둘을 같은 chip 내에서 만들려면 공정비용이 2~3배 증가하며 공정 난이도가 상승하기 때문에 거의 불가능하다.

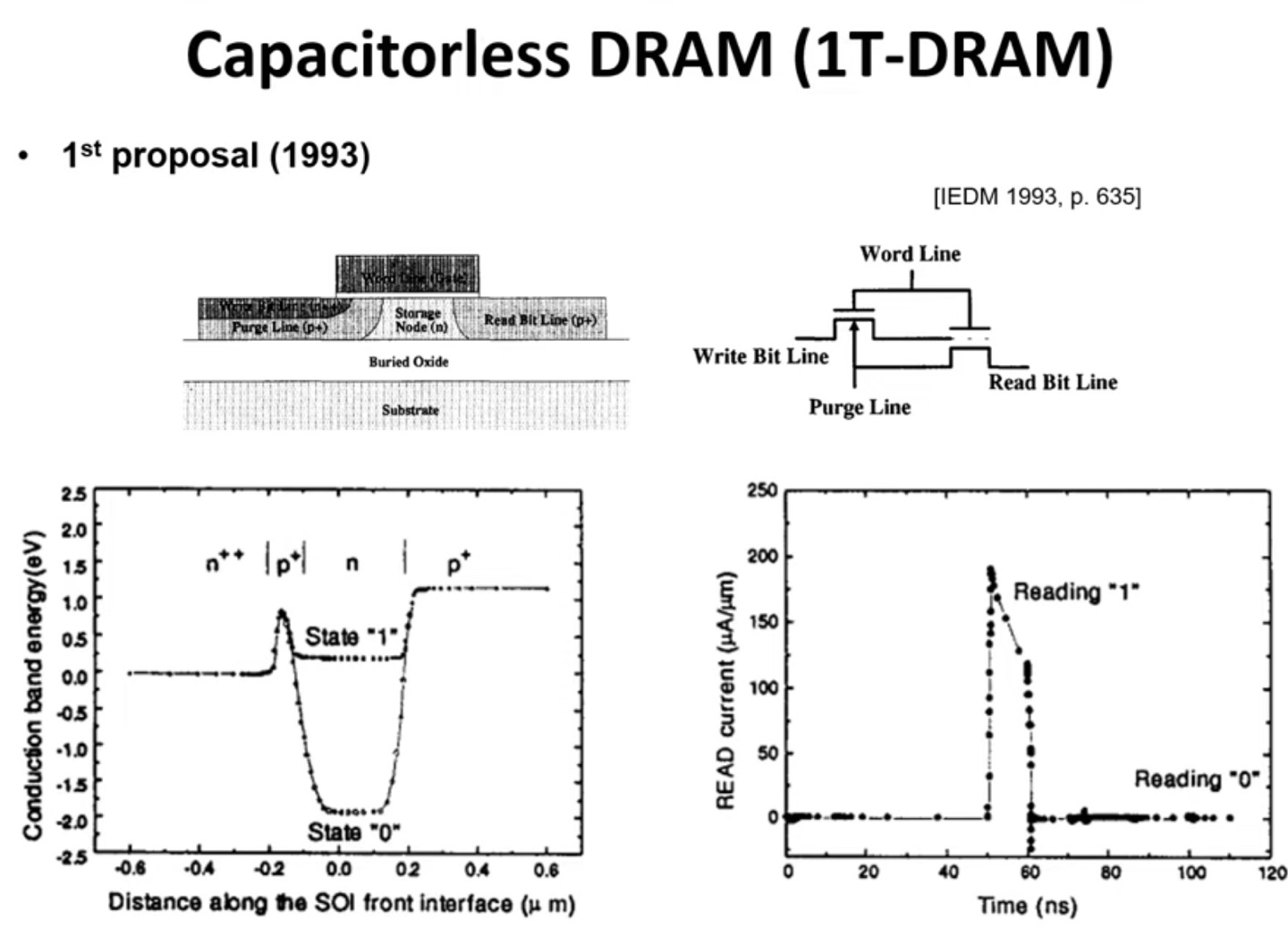

따라서 Capacitorless DRAM (1T-DRAM)이라는 개념이 1993년에 처음 (1T-DRAM) 등장했다.

이는 SOI wafer위에서 만들어진다.

SOI wafer위에 floating body → 전자를 저장했다 읽는 방식으로 한다.

초기의 1T DRAM → npnp 구조를 갖는다.

npn TR과 pnp TR이 있는 효과를 낸다.

왼쪽 TR에 양의전압을 gate에 인가하면 전자가 이동한다→ reverse bias를 인가하여 이동된 전자를 가둔다 : state 1

오른쪽 TR에 전압인가 해서 저장된 전자로 인한 current를 측정한다. → READ current : 전하가 저장되어있으면 1, 아니면 0으로 읽는다.

이를 통해 DRAM의 역할을 할 수 있다.

하지만 실제로 실험적으로 구현된 것은 2000년대가 넘어서 발표되었다.

SOI wafer가 대중화된 시점이 2000년대여서 인 것 같다.

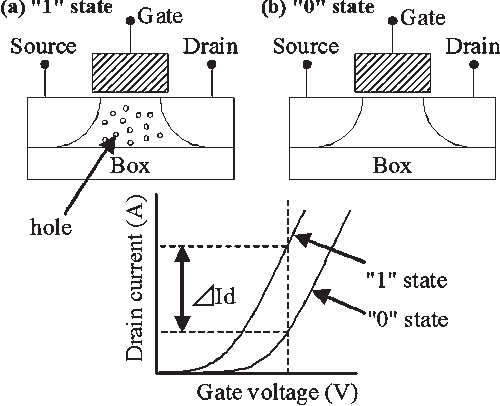

impact ionization mechanism을 사용으며, drain에 높은 전압을 인가하여 e-h쌍이 발생하고, 전자는 drain, hole은 potential이 낮은 substrate으로 빠져나간다.

하지만 oxide층으로 carrier의 움직임이 제한되어 있기 때문에 결과적으로 hole들이 body쪽에 쌓인다.

따라서 쌓인 홀들이 gate전압과 같은 역할을 하기 때문에 drain전류가 더욱 증가한다.

이러한 메커니즘으로 같은 gate전압에서 더 높은 current가 측정되면 1, 아니면 0으로 구분한다.

정리

- impact ionization을 이용하여 추가적인 hole들을 만든다.

- SOI wafer의 floating body영역에 쌓이게 된다.

- 쌓인 hole들이 drain current에 영향을 준다.

- drain current의 측정을 통해 hole들이 쌓여있는지, 없는지를 확인한다.

- drain current가 높고 낮음을 통해 1과 0을 구분한다.

excess carrier이기 때문에 시간이 지나면서 recombination 된다.

일정 시간이 지나면 data가 사라진다 → 휘발성 특성을 갖는다.

impact ionization을 일으킬 수 있는 pulse를 인가 → 1

다시 돌아오게 할 수 있는 pulse를 인가 → 0

하지만 높은 drain bias와 상당히 많은 수의 chip이 소모되는 것을 고려했을 때, 전력소모 문제가 발생한다.

(power consumption)

또한 impact ionization 방식 상 hot carrier가 반드시 발생하며 이는 oxide층에 안좋다.

→ 소자의 신뢰성문제에서 자유롭지 못하다.

이것을 보완하기 위해서 다른방식의 Capacitorless DRAM이 제시되었다.

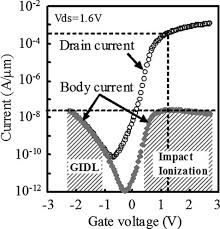

GIDL current을 이용하는 1T DRAM

gate에 음의 전압을 걸었을 때 발생하는 누설전류가 GIDL current이다. : e-h pair 발생

전력소모가 10000배정도 적다.

sensing margin이 적다. ←0과 1차이의 차이

충돌이온화 방식보다 e-h쌍의 개수를 적게만든다.

recombination 되어 사라지기 때문에, 1상태를 유지할 수 있는 시간이 짧다. → memory의 상태를 오랫동안 지속할 수 없다.

single transistor latch 방식을 이용한 1T DRAM

impact ionization 방식과 동일

Vd를 impact ionization을 일으키기 위한 조건보다 높이면 쌓인 hole들이 Id 증가한다.

→ impact ionization이 추가적으로 발생한다.

feedback이 걸리는 상황이 발생한다.

(gate전압을 off해도 hole들이 계속해서 생성되기 때문에 feedback이라고 부른다.)

→ on 상태를 계속 유지하다가 어느 시점이 되면 off상태가 된다.

자체적인 feedback으로 인해 hole들이 지속적으로 생성이 되고 유지될 수 있는 상황이 나타난다.

이것은 single transistor latch를 통해 만들어 낼 수 있다.

장점

- sensing margin이 훨씬 증가한다.

- data retention time도 거의 무한대에 가깝다.

- read하는 과정에서 hole들이 일부분 손실되는 것이 일반적이지만 feedback 현상을 통해 보충할 수 있기 때문에 data read 시 Non-destructive하게 할 수 있다. (기존에 쌓인 hole의 양을 유지한다.)

단점

- impact ionization보다 더 높은 전압으로 인해 소자의 신뢰성에 안좋다.

- 소비전력이 높다

그밖에도

- A^2 RAM : 구조적 변화

- MSDRAM (meta-stable DRAM) : gate 두개를 따로 사용하여 coupling을 control 한다.

- Z^2 FET : pnpn의 형태 → impact ionization 없이도 feedback을 만들어낼 수 있다.

형태의 cap less DRAM이 개발 중이다.